Xilinx Programmable Logic Device Design and Development (Basic) Serial 27: Spartan

The GTH module in the Vrtex-6 HXT device has a higher line rate than the GTX, enabling it to achieve the highest performance high speed serial transceiver. GTH has the following characteristics.

Flexible SERDES supports multi-rate applications.

Implement 40G and 100G protocols, etc.

Powerful transmit pre-emphasis and receive equalizer.

The integrated "gearbox" enables flexible coding: 8B/10B, 64B/66B.

Low power consumption: ~220mW (typical) @10.3125Gbit/s.

Meets common standards such as 10/40/100G Ethernet, PCI Express, OC-48, XAUI, SRIO, and HD-SDI.

5.1.9 Ethernet (Ethernet MAC) ModuleVirtex-6 devices have built-in Ethernet MACs that provide seamless chip-to-chip connectivity without the need to consume programmable logic resources. The Ethernet Media Access Controller (MAC) core supports 10/100/1000 Mbit/s data rate, is UNH-compliant and interoperable, and is designed to meet IEEE 802.3 specifications. It can run at 1000 Mbit/s and 100 Mbit/s separately. And 10Mbit/s mode, or configured in tristate mode. Supports IEEE standard MII, GMII, and RGMII protocols to reduce the bus width of external physical interfaces.

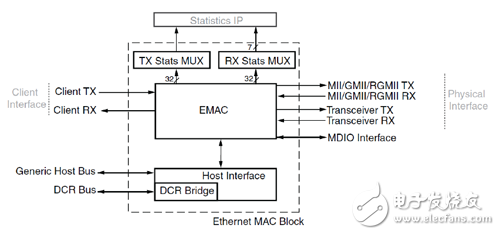

Figure 5-38 shows the block diagram of the Ethernet MAC.

Figure 5-38 Block diagram of the Ethernet MAC

The host can be interconnected to the Ethernet MAC via the host bus or the Device Control Register (DCR) bus.

The physical interface can be configured as MII, GMII, RGMII, SGMII or 100BASE-X, but depending on the physical interface configuration selected, only one set of TX and RX interfaces is activated.

The EMAC has an optional Management Data Input/Output Interface (MDIO) that provides access to the external PHY's management registers and the EMAC's internal physical interface management registers (valid only in 1000BASE-X or SGMII mode configurations).

The EMAC output statistics vector contains the frame information on the Ethernet transmit and receive data paths. The statistic vectors are multiplexed to reduce the number of pins required to connect to the outside world. The statistical IP (StaTIsTIcs IP) is implemented in the FPGA to accumulate the statistical information of the Ethernet MAC transceiving data path.

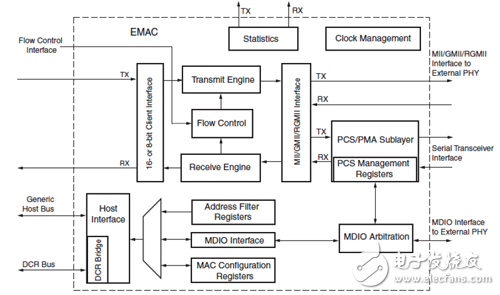

The functional block diagram of the Virtex-6 EMAC is shown in Figure 5-39.

Figure 5-39 Functional Block Diagram of the Ethernet MAC

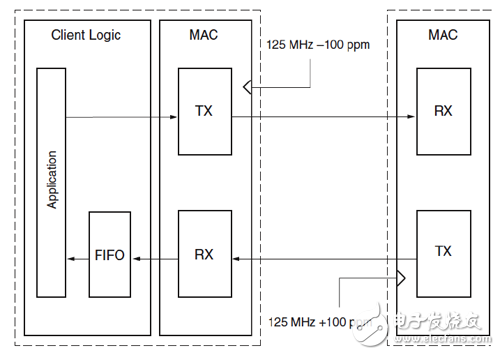

Client interface. It includes the user transmit and receive interface connected to the EMAC accepting sending engine. The data width of the client interface can be configured as 8 or 16 bits, and the default is 8 bits. The flow control interface allows the client to control the physical layer to stop sending frames until the client has the ability to accept more frames. EMAC's flow control is designed according to the IEEE 802.3-2005 standard. The Ethernet MAC can pause and restart the frame transmission after detecting a valid pause frame. The EMAC implements flow control by sending a pause frame for a certain period of time. Figure 5-40 shows the flow control structure.

Figure 5-40 Flow control structure

There is a receive address filter on the EMAC interface path that controls accepting or rejecting incoming frames.

The output statistics vector contains frame statistics on the Ethernet transmit and receive data paths. The transmit statistics vector TX_STATISTICS_VECTOR contains the statistics of the transmitted frame and consists of a 32-bit vector and an internal signal. The acceptance statistics vector RX_STATISTICS_VECTOR contains the statistics of the accepted frame, consisting of a 28-bit vector and an internal signal. The Xilinx CORE Generator software provides an external statistics module free of charge that accumulates all statistics on the Ethernet MAC's transmit and receive data paths.

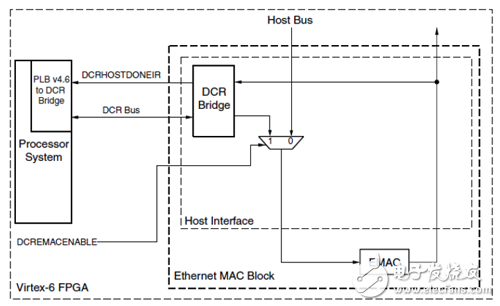

Host/DCR bus interface. The host interface provides access to the EMAC configuration register, the EMAC address filter register, the PCS/PMA sublayer registers, and the MDIO interface to control external devices. The EMAC host interface can be accessed via a general purpose host bus or a DCR bus (when connected to the processor). Figure 5-41 shows the internal structure of the host interface. The Xilinx XPS tool provides the XPS_LL_TEMAC soft core to control EMAC over the PLB bus. The PLB and DCR buses can be switched by bridge.

Figure 5-41 Internal structure of the host interface

MDIO interface. In the 1000BASE-X or SGMII mode, the host interface can access the PCS management registers in the EMAC. The host interface can also access external PHY devices through the MDIO interface. In the case that MDIO is enabled and the host interface is not enabled, the external device can also access the PCS management register in the EMAC in the mode configured to 1000BASE-X or SGMII.

Physical end interface. The physical interface of the Ethernet MAC can be configured as Media Independent Interface (MII), Gigabit Media Independent Interface (GMII), Simplified Gigabit Media Independent Interface (RGMII), Serial Gigabit Media Independent Interface (SGMII), 1000BASE- X. MII, GMII, and RGMII are parallel interfaces that are typically connected to an external physical layer (PHY) chip to provide BASE-T capability at 10/100/1000 Mbit/s, while also supporting a rate of 10/100 Mbit/s. Half-duplex operation and full-duplex operation at various rate conditions. SGMII and 1000BASE-X are serial interfaces that use the PCS and PMA sections of the Ethernet MAC, which are connected to the Virtex-6 RocketIO GTX/GTH serial transceiver. When used with a parallel interface, SGMII provides full-duplex BASE-T capability at 10/100/1000 Mbit/s. This serial interface greatly reduces the number of pins connected to the external PHY chip. When the EMAC is configured in 1000BASE-X mode, the PCS/PMA module works with the RocketIO transceiver to provide all the connectivity needed for a direct connection to a Gigabit converter (GBIC) or a small form-factor pluggable (SFP) fiber optic transceiver. Features. This avoids the need for an external PHY chip for 1000BASE-X network applications. When configured in MII/GMII/RGMII mode, the external physical chip PHY can be accessed using standard IO; when configured in 1000BASE-X or SGMII mode, the PCS/PMA submodule in the MAC is enabled, and the EMAC is connected through the PCS/PMA submodule. Line transceiver GTX.

Clock management module. This module automatically configures the correct output clock based on the speed of the Ethernet MAC (10Mb/s, 100Mb/s or 1000Mb/s) and mode (GMII, MII, RGMII, SGMII, and 1000BASE-X).

The EMAC module can be used in the design by calling the primitive of the Ethernet MAC or by using the CoreGen tool to configure the EMAC parameters.

5.1.10 PCIe Endpoint Module

Panel Mount Power Quality Meter,Ac Western Power Meter Panel,3 Phase Kwh Energy Panel Meter,Power Meter For Electrical Panel

Jiangsu Acrel Electrical Manufacturing Co., LTD. , https://www.acrel.com.pk